10 Gaussian Blur

10 : Gaussian Blur

- Author: Alfonso Cortes

- Description: 4-bit gaussian blur filter

- GitHub repository

- Clock: 100000 Hz

How it works

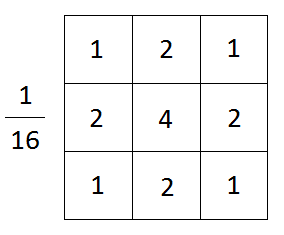

This filter receives nine 4-bit pixels in a free-running shift register and performs a gaussian blur, returning the value of the middle pixel. The weights are as shown below.

How to test

Input the pixel value and its neighborhood (nine pixels) from left to right, top to bottom. Once the shift register is full (after nine clock cycles) the output can be sampled. The last stage of the shift register is also available at the output for testing purposes.

External hardware

An FPGA should be useful.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | reg_in[0] | reg_out[0] | |

| 1 | reg_in[1] | reg_out[1] | |

| 2 | reg_in[2] | reg_out[2] | |

| 3 | reg_in[3] | reg_out[3] | |

| 4 | blur[0] | ||

| 5 | blur[1] | ||

| 6 | blur[2] | ||

| 7 | blur[3] |